TP 2 MODUL 2

TP 1 MODUL 2

1. Kondisi [kembali]

2. Gambar Rangkaian [kembali]

3.Video Simulasi [kembali]

4.Prinsip Kerja [kembali]

JK Flip-Flop Sesuai pada kondisi rangkaian memiliki J-K flip flop dan D flip flop dengan inputan berupa saklar SPDT dan output berupa logicprobe. Pada rangkaian ini B1 bernilai 1 karena terhubung dengan vcc, B2 bernilai 0 karena dihubungkan dengan ground, B3 dan B4 bernilai 1 karena dihubungkan dengan vcc, dan B0 bernilai 0 karena dihubungkan dengan ground.

B1 dihubunkan dengan inputan JK Flip Flop input S, B2 dihubungkan dengan inputan J, B3 dihubungkan dengan inputan CLK, B4 dihubungkan dengan inputan K dan B0 dihubungkan dengan inputan R.

Untuk nilai pada JK Flip Flop sendiri didapat berdasarkan tabel kebenaran yang mana dikarenakan nilai S bernilai 1 dan nilai R bernilai 0. Sehingga nilai CLK itu dont care yang mana berapapun nilai output maka tidak akan mempengaruhi nilai CLK, dan Q bernilai 1 sedangkan Q' yang merupakan invers dari Q bernilai 0.

D Flip-Flop

B5 dihubungkan pada input D dalam D Flip-flop, B6 dihubungkan dengan inputan CLK. Dan B1 dihubungkan dengan inputan S pada D Flip-Flop serta B0 dihubungkan dengan inputan R.

Terlihat pada rangkaian ini nilai S=1, R=0. berdasarkan tabel kebenaran untuk S=1 dan R=0 maka nilai D bersifat dont care yang mana artinya nilai D tidak akan mempengaruhi output. Untuk nilai CLK juga sama bersifat dont care dan Q bernilai 1 serta Q' adalah invers dari Q maka bernilai 0.

Sedangkan untuk tabel kebenaran dari masing masing IC adalah sebagai berikut:

1. J-K Flip-Flop (4027)2. D Flip-Flop (4013)

5.Link Download [kembali]

File Proteus Disini

Flip-Flop

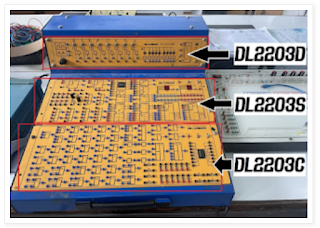

- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

- Jumper

|

Laporan Akhir 2 Modul 1

Rangkaian Sederhana 1:

Pada percobaan ini kita menggunakan prinsip Al-Jabar Bolean, yang mana nantinya nilai output akan dibuktikan dengan perhitungan secara manual.

Dalam percobaan ini kita menggunakan 3 input yang masuk kedalam gerbang AND yaitu A, D dan C' dan 2 input gerbang XOR yaitu B, D. yang mana nantinya output dari kedua gerbang ini akan memasuki kaki input OR.

Rangkaian Sederhana 2:

Pada percobaan ini kita menggunakan prinsip Al-Jabar Bolean, yang mana nantinya nilai output akan dibuktikan dengan perhitungan secara manual.

Dalam percobaan ini kita menggunakan 3 input yang masuk kedalam gerbang AND yaitu A, B' dan C dan 2 input gerbang XOR yaitu B, D. yang mana nantinya output dari kedua gerbang ini akan memasuki kaki input OR.

Nilai input dilihat dalam indikator jurnal yang telah disediakan. Kedua rangkaian akan menhasilkan output yang sama dan untuk alasan mengapanya telah dijawab dalam soal analisa.

Gerbang yang digunakan pada percobaan 2:

Gerbang XOR

Adalah gerbang logika yang menggunakan prinsip penjumlahan ekslusif, dimana jika hasil penjumlahan input bernilai ganjil maka output bernilai 1 begitu juga sebaliknya.

Gerbang AND

Adalah gerbang logika yang memakai prinsip perkalian, jika semua input 1 maka otomatis 1 x 1 =1 begitu juga dengan 0 x 0 =0.

Gerbang OR

Adalah gerbang logika yang memakai prinsip penjumlahan, dimana jika semua input 1 maka 1+1= 0 begitu juga dengan 0 maka 0+0 = 0.

k. 0+0+0=0

Laporan Akhir 1 Modul 1

- Panel DL 2203D

- Panel DL 2203S

- Panel DL 2203C

- Jumper

Pada percobaan ini kita menggunakan module D'Lorenzo pada bagian DL2203D dan DL2203C. Pada bagian DL2203D, kita memasukkan logika dari B0 dan B1 yang kemudian dihubungkan ke gerbang logika menggunakan jumper. Logika B0 dan B1 disini kita set sesuai dengan perintah pada modul percobaan,

- Gerbang NOT

- Gerbang AND

- Gerbang OR

- Gerbang XOR

- Gerbang NAND

- Gerbang NOR

- Gerbang XNOR

1. Analisa perbedaan saat B1 dhubungkan ke clock dengan B1 dihubungkan ke switch

7. Link Download [Kembali]

TP 2 MODUL 1

1. Kondisi [kembali]

- Rangkaian Sederhana 1: B=1, D=0, A=0,C'=1, D=1

- Rangkaian Sederhana 2: B=1, D=0, A=1, B=1, C'=0

2. Gambar Rangkaian [kembali]

3.Video Simulasi [kembali]

4.Prinsip Kerja [kembali]

Rangkaian Sederhana 1:

Sesuai denan kondisi yang sudah dipilih pada modul 1, pada rangkaian ini kita menggunakan 5 Switch SPDT yang dimana salah satu kaki dihubungkan pada vcc dan kaki lainnya diubungkan pada ground. Kaki yang dihubungkan ke vcc akan bernilai 1(Aktif) sedangkan kaki switch yang dihubungkan pada kaki ground akan bernilai 0(Mati). Switch 1 yaitu B outputnya bernilai 1 karena dihubunkan pada VCC. Output yang bernilai 1 masuk kedalam kaki input erbang XOR U1:A. Dan Switch 2 yaitu D terhubung pada round yang menghasilkan nilai 0 masuk kedalam kaki input gerbang logika XOR U1:A. karena kedua input bernilai 0 dan 1 serta berdasarkan prinsip kerja XOR yaitu penjumlahan ekslusif yaitu jika hasil penjumlahan input bernilai genap maka nilai output akan bernilai 0 begitu sebaliknya. Dikarenakan hasil penjumlahan kaki input XOR U1:A bernilai ganjil sehinga hasil outputnya adalah 1. Output ini memasuki kaki input OR. Switch 3 yaitu C' bernilai 1 dikarenakan dihubunkan pada VCC. Output ini dihubungkan dengan input gerbang logika NOT U4:A sehingga menghasilkan output 0. Dikarenakan prinsip aksen atau bar, maka hasil yang dibaca bukanlah 0 melainkan 1. Output 1 ini mengalir masuk kedalam kaki input erbang logika AND U2:A. Switch A memiliki output 0 dikarenakan terhubung dengan ground. Output 0 ini mengalir memasuki kaki input gerbang logika AND U2:A. Switch 5 yaitu D bernilai 1 dikarenakan terhubung pada VCC. Output 1 ini mengalir memasuki kaki input gerbang logika AND U2:A. Karena ketiga input bernilai 0,0,1. Berdasarkan prinsip AND yaitu perkalian maka output yang dihasilkan adalah 0. Output 0 ini mengalir memasuki kaki input gerbang logika OR. Karena kedua input pada gerbang OR bernilai 1 dan 0 maka berdasarkan prinsip OR yaitu penjumlahan maka output yang dihasilkan adalah 1. Output ini mengalir melalui hambatan 220V yang mana mampu menghidupkan LED.

Rangkaian Sederhana 2:

Switch 6 yaitu B bernilai 1 karena dihubungkan pada VCC. Output yang dihasilkan mengalir melalui kaki input gerbang logika XOR U1:B. Switch 7 yaitu D bernilai 0 dikarenakan dihubungkan pada ground. Output yang dihasilkan mengalir masuk kedalam kaki input erbang logika XOR U1:B. berdasarkan prinsip gerbang logika XOR yaitu penjumlahan ekslusif, maka output yang dihasilkan adalah 1. Output ini mengalir masuk kedalam kaki input erbang logika OR.

Switch 8 yaitu A bernilai 1 karena dihubunkan pada VC. Output yang dihasilkan mengalir masuk kedalam kaki AND U2:B. Switch 9 yaitu B menhasilkan output 1 diakrenakan dihubungkan pada VCC. Output 1 ini akan masuk kedalam kaki input gerbang AND U2:B. Switch 10 yaitu C' memiliki output 0 dikarenakan dihubungkan pada ground. Output 0 ini memasuki kaki NOT U4:B yang menhasilkan output 1 berdasarkan prinsip aksen atau bar maka output yang dibaca bukanlah 1 melainkan 0. Dikarenakan seluruh input gerbang logika U2:B berilai 1 dan berdasarkan prinsip AND yaitu perkalian maka output yang dihasilkan adalah 1. Output ini mengalir masuk kedalam kaki input gerbang logika OR.

Karena kedua input bernilai 1 maka berdasarkan prinsip OR atau penjumlahan maka output yang dihasilkan adalah 1.

5.Link Download [kembali]

File Proteus Disini

TP 1 MODUL 1

1. Kondisi [kembali]

2. Gambar Rangkaian [kembali]

3.Video Simulasi [kembali]

4.Prinsip Kerja [kembali]

Sesuai dengan kondisi yang telah dipilih pada modul 1, pada rangkaian ini kita menggunakan 4 switch SPDT yang dimana salah satu kaki dihubungkan pada vcc dan kaki lainnya dihubungkan pada ground. Kaki yang dihubungkan ke vcc akan bernilai 1(Aktif) sedangkan kaki switch yang dihubungkan pada kaki ground akan bernilai 0(Mati). Setelah itu pada Switch 1 outputnya bernilai 0 dan masuk kedalam kaki input logic gate AND U1:B, karena ini gerbang logika AND dimana menunakan prinsip perkalian, dikarenakan seluruh inputnya 0 maka output dari logic gate U1:B juga akan bernilai 0. Output ini akan mengalir memasuki kaki input gerbang logika XOR U5:A. Dikarenakan seluruh input yang masuk kedalam gerbang logika XOR U5:A berjumlah genap maka hasil output yang dihasilkan adalah 0. Lalu output ini akan masuk kedalam salah satu input gerbang logika NOR dengan 3 input. Switch 2 outputnya akan bernilai 0 karena dihubungkan pada ground. Output dari kaki Switch 2 ini akan masuk kedalam input gerbang logika AND U1:A. Dikarenakan seluruh inputnya 0 dan berdasarkan prinsip dari gerbang logika AND adalah perkalian maka output yang dihasilkan juga bernilai 0. Output dari gerbang AND U1:A akan mengalir masuk kedalam kaki input gerbang XNOR U6:A. Karena seluruh input bernilai 0 dan berdasarkan prinsip XNOR yaitu invers dari pernjumlahan ekslusif XOR maka input yang berjumlah genap akan menghasilkan output yan bernilai 1. Output dari gerbang XNOR ini akan mengalir pada salah satu kaki gerbang NOR dengan 3 input. Switch 3 dan Switch 4 outputnya akan bernilai 0 karena dihubungkan pada ground. Output dari Switch 3 akan dialirkan masuk kedalam kaki input gerbang logika AND U2:A. Dikarenakan seluruh input pada gerbang AND bernilai 0 maka berdasarkan prinsip gerbang AND yaitu perkalian maka outputnya akan bernilai 0. Output ini akan mengalir masuk kedalam kaki NOR 4 input. Karena seluruh input pada grbang NOR adalah bernilai 0 dan berdsarkan prinsip dari gerbang NOR yaitu invers dari OR maka output yang dihasilkan adalah 1. output ini akan mengalir masuk ke kaki input NOR 3 input. Karena seluruh Switch sudah masuk kedalam kaki input gerbang logika NOR 3 input. Maka input yang dihasilkan adalah 0,1,1. Berdasarkan prinsip dari NOR adalah invers dari OR (Penjumlahan), maka output yang dihasilkan adalah 0.

5.Link Download [kembali]

File Proteus Disini

Modul 4

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Pendahuluan 2. Tujuan 3. Alat dan Bahan 4. Dasar Teori 5. Percobaan Percob...

-

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Pendahuluan 2. Tujuan 3. Alat dan Bahan 4. Dasar Teori 5. Percobaan Percob...

-

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Jurnal 2. Alat dan Bahan 3. Rangkaian Simulasi 4. Prinsip Kerja Rangkaian 5. ...